学习视频

SDRAM介绍

同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM)是有一个同步接口的动态随机存取内存(DRAM)。通常DRAM是有一个异步接口的,这样它可以随时响应控制输入的变化。而SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。时钟被用来驱动一个有限状态机,对进入的指令进行管线(Pipeline)操作。这使得SDRAM与没有同步接口的异步DRAM(asynchronous DRAM)相比,可以有一个更复杂的操作模式。

SDRAM从发展到现在已经经历了五代,分别是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代,DDR4 SDRAM。

SDRAM操作时序

- 在对 SDRAM进行读写操作之前需要先对芯片进行初始化;SDRAM读写是一个较为复杂的控制流 程,其中包括行激活、列读写、预充电、刷新等一系列操作。

初始化

初始化流程如下

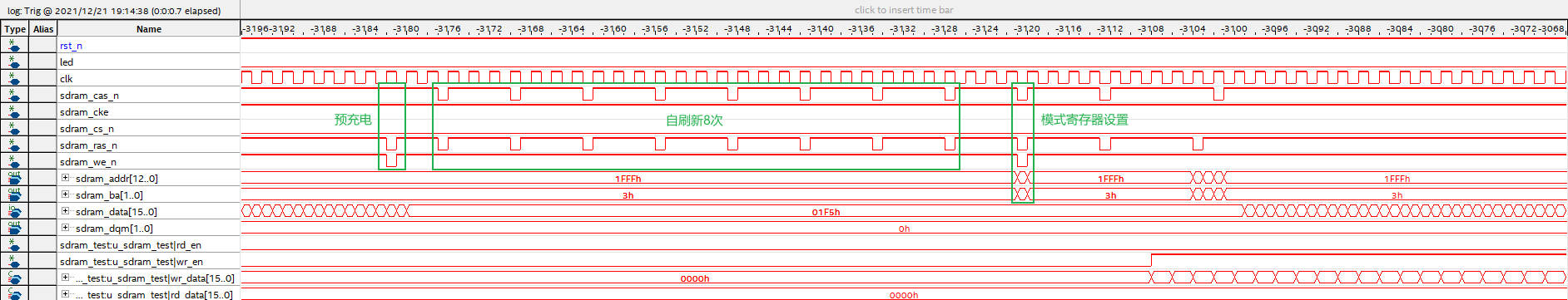

SDRAM上电后要有200us的输入稳定期,在这个时间内不可以对SDRAM的接口做任何操作; 200us结束以后给所有L-Bank预充电,然后是连续8次刷新操作;最后设置模式寄存器。初始化 最关键的阶段就在于模式寄存器(MR,Mode Register)的设置,简称MRS(MR Set)。模式寄存器如下

如上图所示,用于配置模式寄存器的参数由地址线提供,地址线不同的位分别用于表示不 同的参数。SDRAM通过配置模式寄存器来确定芯片的工作方式,包括突发长度(Burst Length)、 潜伏期(CAS Latency)以及操作模式等。

需要注意的是,在模式寄存器设置指令发出之后,需要等待一段时间才能够向SDRAM发送 新的指令,这个时间我们称之为模式寄存器设置周期tRSC(Register Set Cycle)。

行激活

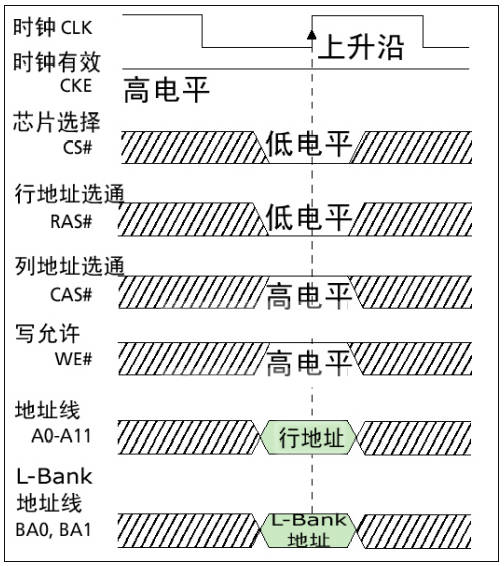

- 行激活时序图

初始化完成后,无论是读操作还是写操作,都要先激活(Active)SDRAM中的一行,使之 处于活动状态(又称行有效)。在此之前还要进行SDRAM芯片的片选和L-Bank的定址,不过它 们与行激活可以同时进行。

在片选CS#(#表示低电平有效)、L-Bank定址的同时,RAS(Row Address Strobe,行地址选通脉冲)也处于有效状态。此时An地址线则发送具体的行地址。如图中是A0-A11,共有12个地址线,由于是二进制表示法,所以共有4096个行(2^12=4096),A0-A11的不同数值就确定了具体的行地址。由于行激活的同时也是相应L-Bank有效,所以行激活也可称为L-Bank有效。

列读写

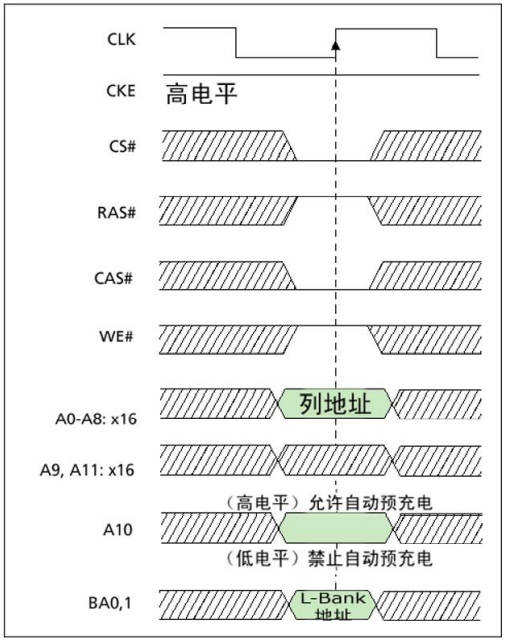

- 列选通与读操作时序图

由于在SDRAM中,地址线是行列共用的,因此列寻址时地址线仍然是A0-A11。在寻址时,利用RAS(Row Address Strobe,行地址选通脉冲)与CAS(Column Address Strobe,列地址选通脉冲)来区分行寻址与列寻址。 - 在发送列读写命令时必须要与行激活命令有一个时间间隔,这个间隔被定义为tRCD, 即RAS to CAS Delay(RAS至CAS延迟)。这是因为在行激活命令发出之后,芯片存储阵列电子 元件响应需要一定的时间。tRCD是SDRAM的一个重要时序参数,广义的tRCD以时钟周期(tCK, Clock Time)数为单位,比如tRCD=3,就代表RAS至CAS延迟为三个时钟周期,如图 33.1.8所 示。具体到确切的时间,则要根据时钟频率而定。

数据输出(读)

- 在选定列地址后,就已经确定了具体的存储单元,剩下的事情就是数据通过数据I/O通道(DQ)输出到内存总线上了。但是在CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定义为CL(CAS Latency,CAS潜伏期)。CL时间越短,读数据时SDRAM响应就越快。由于CL只在读取时出现,所以CL又被称为读取潜伏期(RL,Read Latency)。CL的单位与tRCD一样,为时钟周期数,具体耗时由时钟频率决定。

数据输出(写)

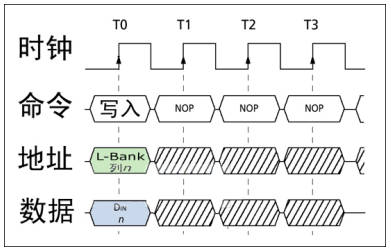

- 数据写入时序图

数据写入的操作也是在tRCD之后进行,但此时没有了CL(记住,CL只出现在读取操作中), 行寻址与列寻址的时序图和上文一样,只是在列寻址时,WE#为有效状态。

数据与写指令同时发送。不过,数据并不是即时地写入存储单元,数据的 真正写入需要一定的周期。为了保证数据的可靠写入,都会留出足够的写入/校正时间(tWR, Write Recovery Time),这个操作也被称作写回(Write Back)。tWR至少占用一个时钟周期 或再多一点(时钟频率越高,tWR占用周期越多)。

此外

- 除上述操作之外,还有突发长度、预充电、刷新、数据掩码常用操作,具体可以查阅《开拓者FPGA开发指南》SDRAM读写测试实验。

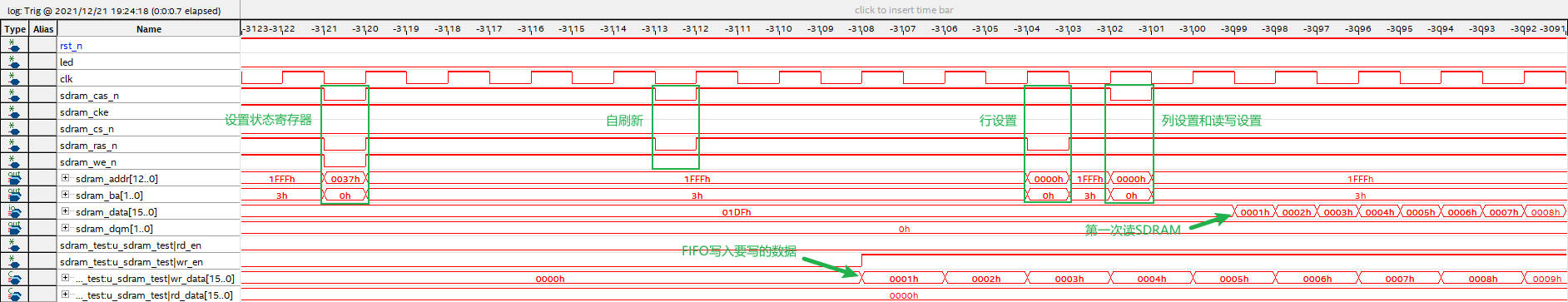

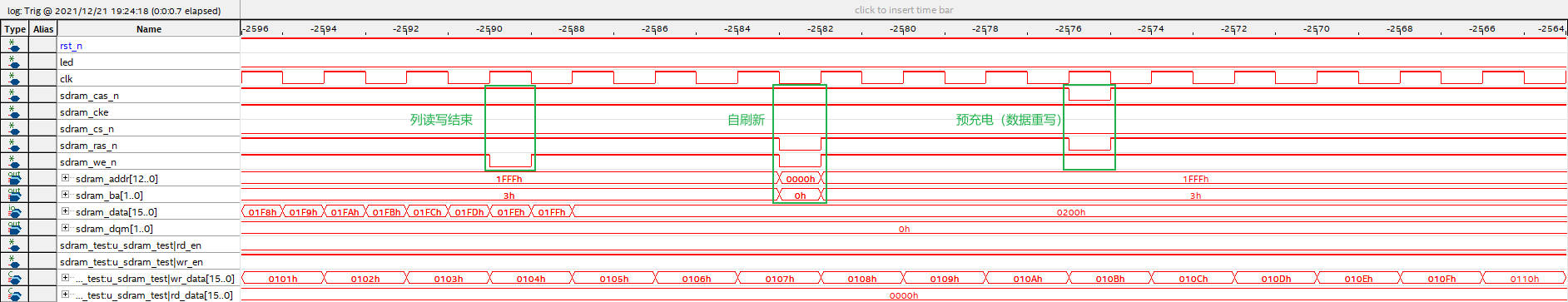

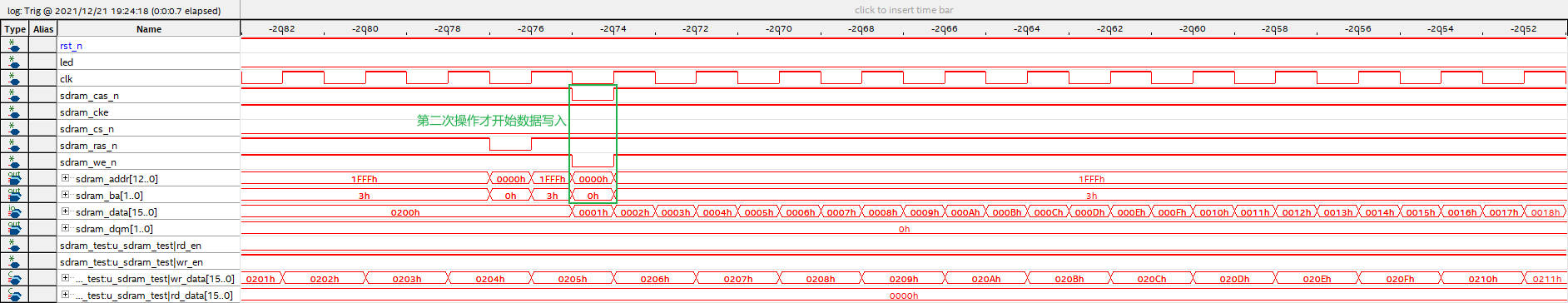

实验仿真