好久不见,甚是想念

一个多月没写博客了,毕业后学习时间少了,白天忙公司的项目,偶尔晚上有空看看自己想学的资料,自己还在做个地质分析仪的项目,每周日会花一天的时间做。为自己加油,2022年我还要完成这块FPGA的学习,感谢那位支持我学这块开发板的人。

安装Vivado

- 下载vivado安装包,资料链接B盘:https://pan.baidu.com/s/1eM7Sx-RmeYFE1ht_RPqxhw 提取码:a8vu

- 解压安装包到无中文路径的目录下,否则会出现安装包无法打开的情况。打开安装包,我在安装选件的页面取消了K系列、V系列和Soc Zynq的选件,安装空间要70GB左右,因此我还买了个1T的固态。

- 激活只需要网上下载对应版本的激活licences,在激活页面load a licences即可。

软件操作

- Tools -> Settings -> Text Editor中选择编辑器,我选择的是notepad++,需要将编辑器路径加到系统环境变量。

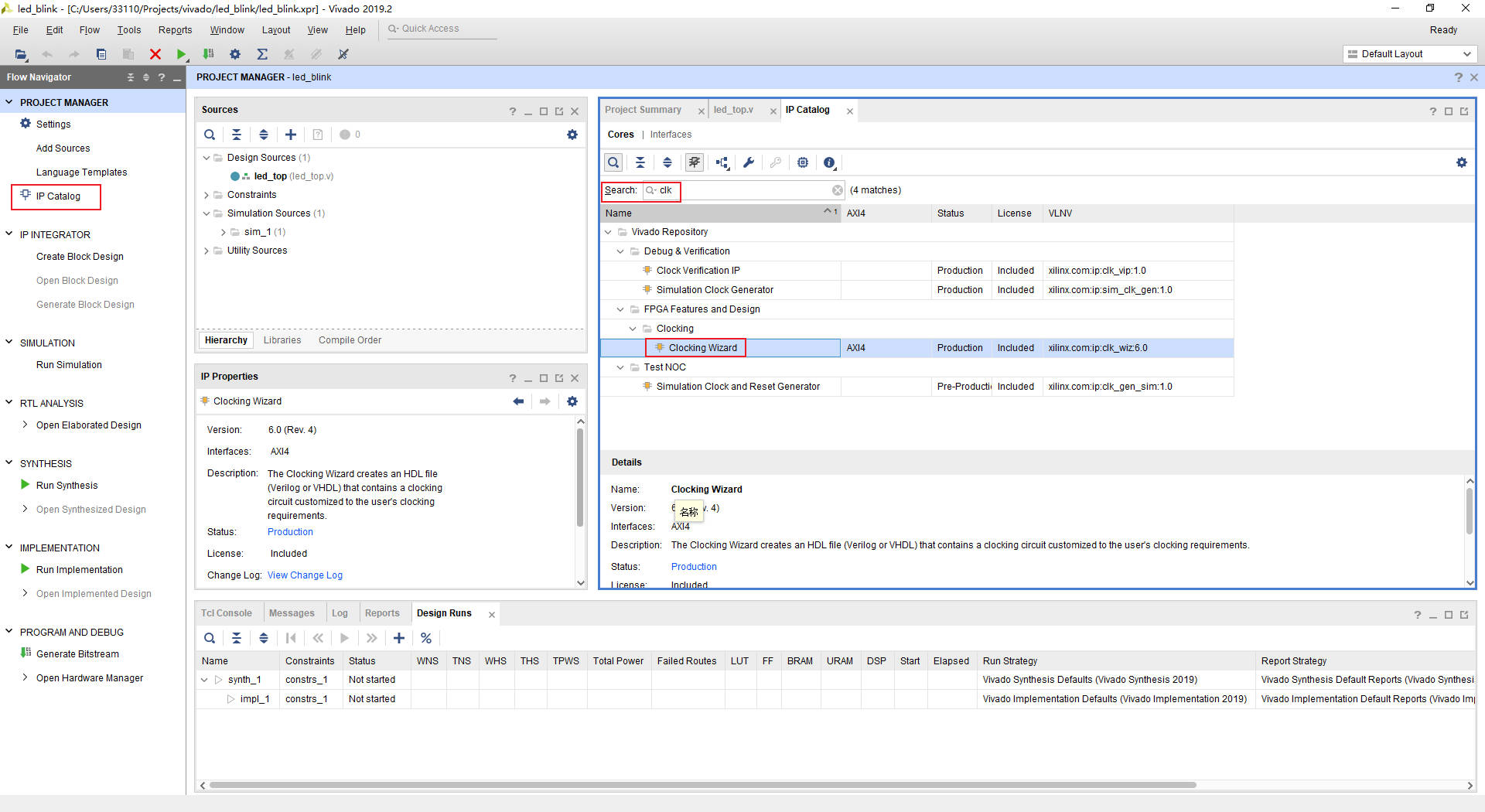

- 创建PLL IP核:

- 功能仿真,RTL分析,综合,约束输入,设计实现都在左侧的Flow Navigator中。

流水灯

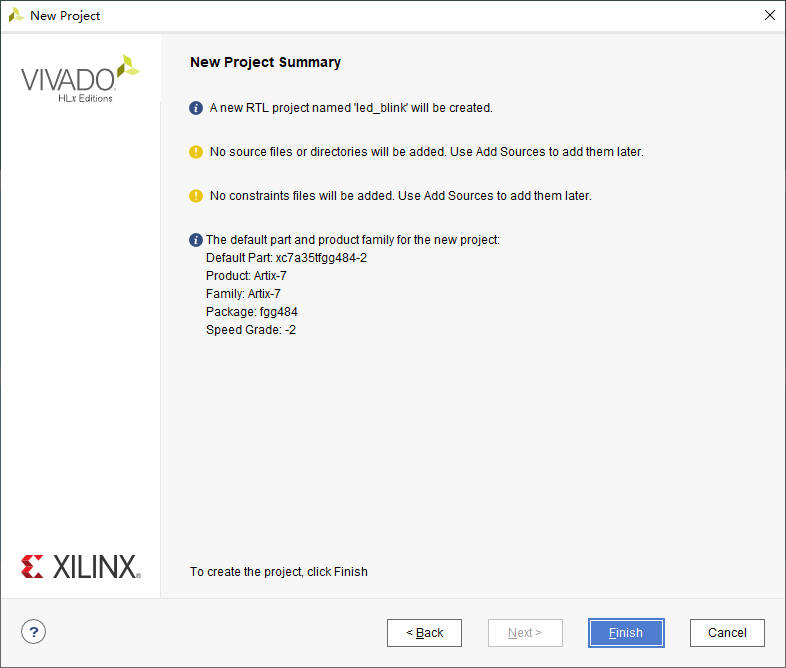

- New Project,芯片选择xc7a35tfgg484-2。

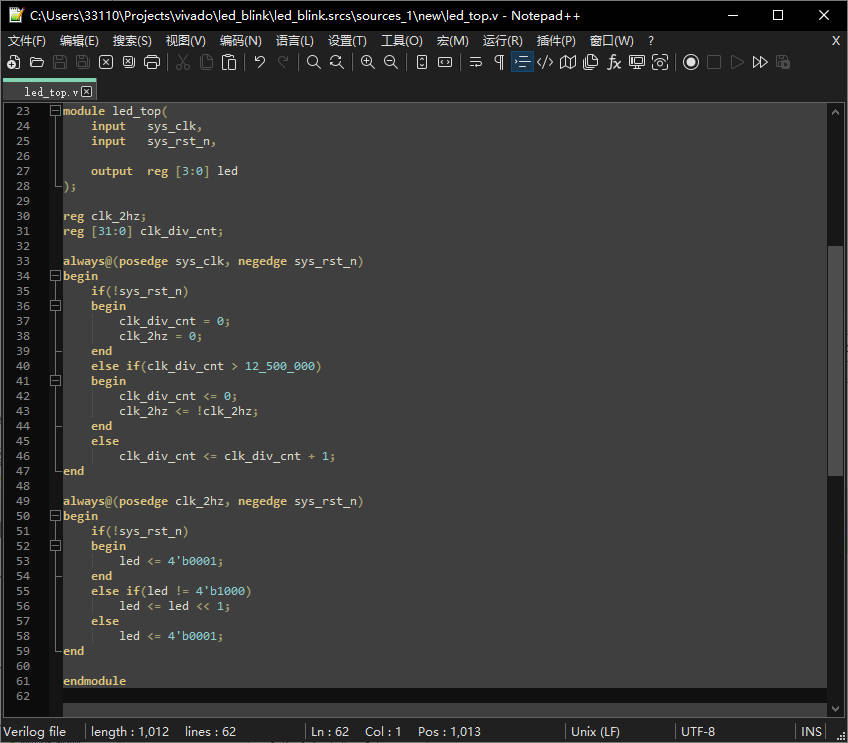

- Add Sources -> Create File,创建led_top.v文件。

- Vivado中打开文件会调用Notepad++编辑器,编写流水灯代码:

- 再功能仿真(可选),再综合、约束输入。

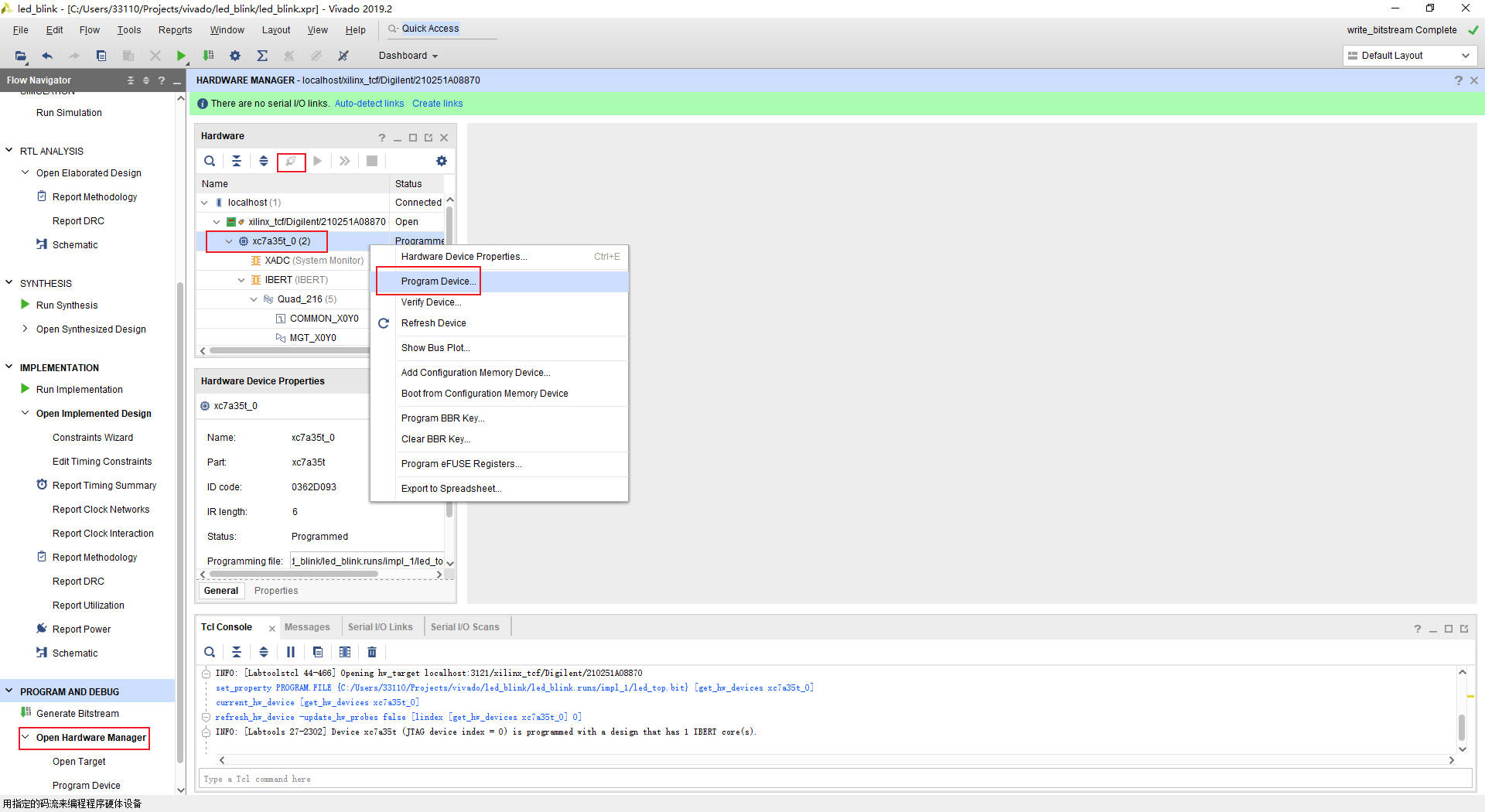

- 最后生成bit流下载到开发板:

- Xilinx的集成开发环境要比Altera的好用不少,就是编译速度较慢。